NPU HW/SW Co-Design

NPU HW/SW Co-DesignAbout

With the rapid growth of deep learning application areas, the support of hardware that can efficiently accelerate these processes has become increasingly important. Consequently, the development of Neural Processing Units (NPUs) for energy-efficient AI acceleration has been gaining momentum. However, traditional hardware design approaches, which start software development only after hardware development is completed, have several issues. If hardware design flaws or low performance are discovered, the entire design process must begin anew, and software development also becomes complex and time-consuming.

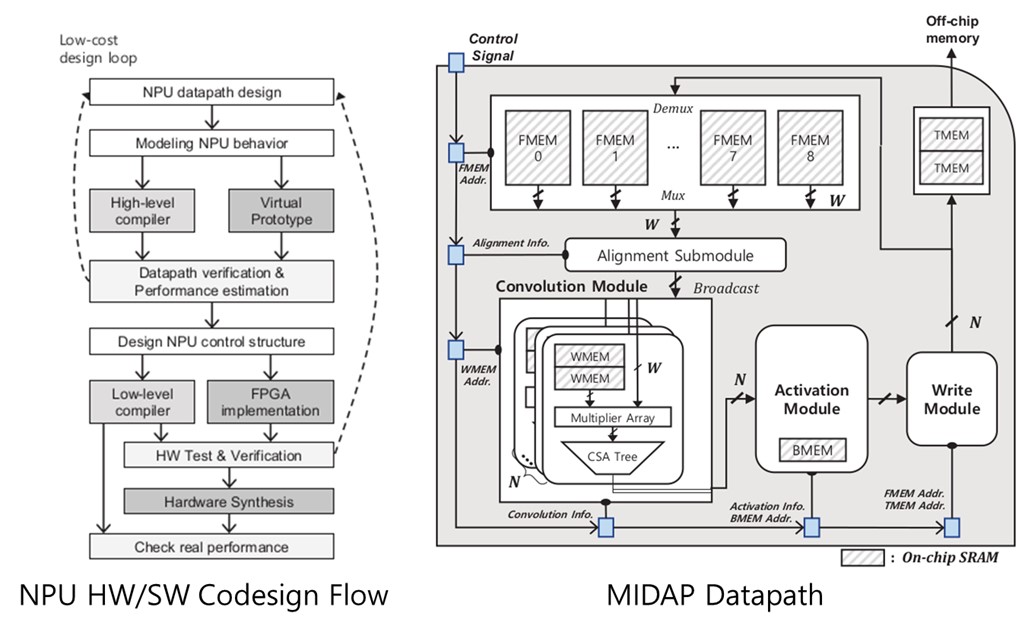

To address these issues, our lab proposes an integrated hardware/software design methodology for NPUs. The key to this methodology is to simultaneously progress hardware and software development, reducing the design iteration cycle. We have enabled performance prediction of software without actual hardware through virtual prototyping. This approach not only allows compiler developers to easily predict software performance, but also facilitates the exploration of various NPU architectures using a hardware simulator implemented in software.

Using this methodology, we have designed MIDAP, an energy-efficient CNN accelerator. It is designed with a fully pipelined structure and integrates large SRAM banks to minimize resource contentions and DRAM access. Additionally, it supports various non-convolutional operations and aims to maximize final performance and MAC utilization by standardizing data formats for easier software development.

So far, we have conducted system-level simulations, software development through virtual prototyping, NPU compiler development, datapath and control structure design, RTL-level hardware design, and FPGA verification, and are now in the stage of actual chip fabrication. Remarkably, thanks to our hardware/software co-design methodology, the simulator, compiler, and datapath design were all developed by a team of just two individuals within a span of two years, showcasing the effective progression of our NPU development process.